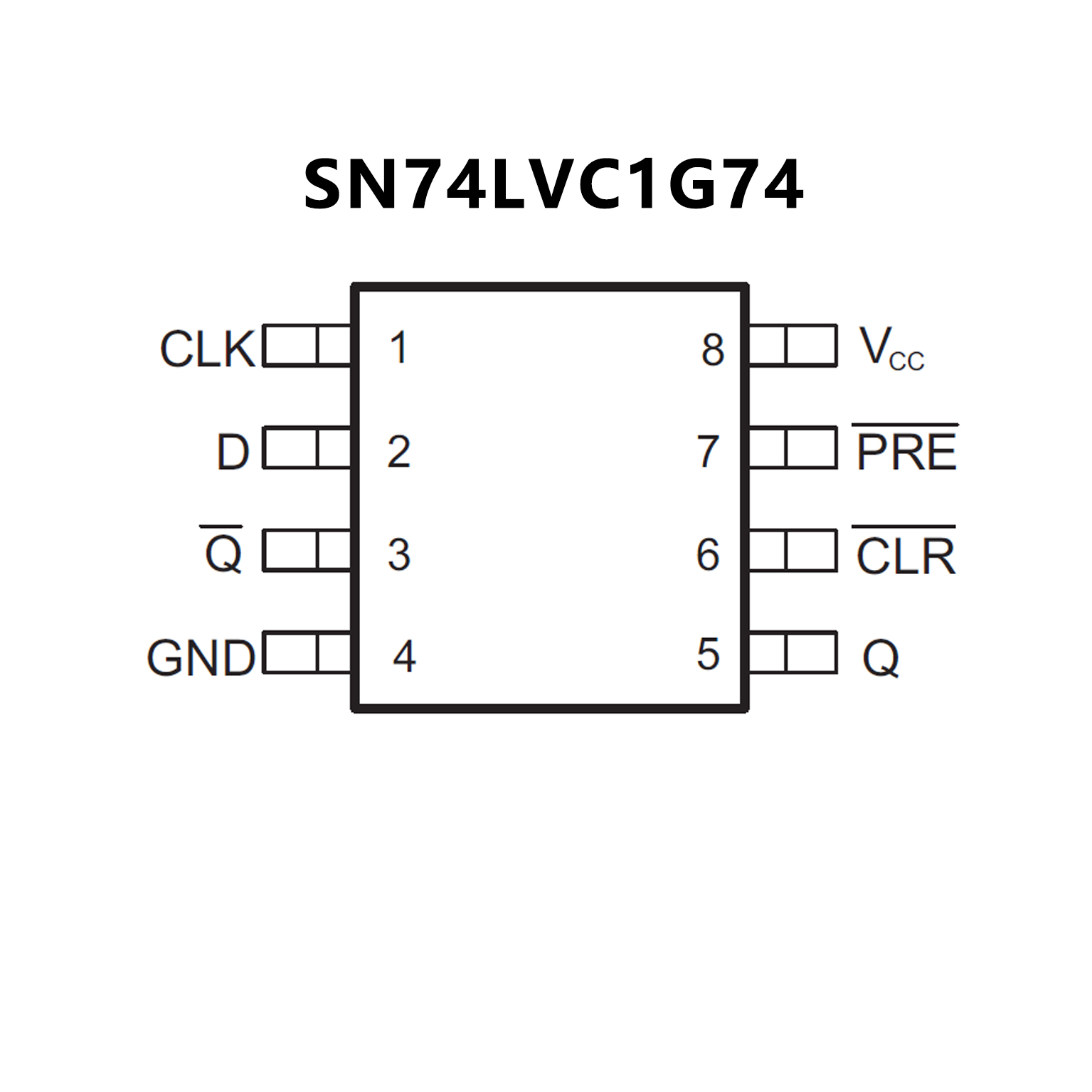

Single Positive Edge Triggered D Type Flip Flop with Clear and Preset, 74LVC1G74XVS8G P2P SN74LVC1G74

优势替代

FEATURES

? Available in the Texas Instruments

NanoFree? package

? Supports 5-V VCC operation

? Inputs accept voltages to 5.5-V

? Supports down translation to VCC

? Maximum tpd of 5.9-ns at 3.3-V

? Low power consumption, 10-?A maximum ICC

? ±24-mA output drive at 3.3-V

? Typical VOLP (output ground bounce)

0.8-V at VCC = 3.3-V, TA = 25°C

? Typical VOHV (output VOH undershoot)

2-V at VCC = 3.3 V, TA = 25°C

? Ioff supports live insertion, partial-

power-down mode, and back-drive protection

? Latch-up performance exceeds 100 mA

per JESD 78, class II

? ESD protection exceeds JESD 22

2000-V human-body model

200-V machine model

1000-V charged-device model

PIN CONFIGUTION

74LVC1G74XVS8G.pdf

74LVC1G74XVS8G.pdf